# Undesirable Sub-harmonic Currents in the Coil of Buck Converter Prototype - Project Bumblebee

Jacek Kaczmarek, Robert Suszynski Department Electronics and Computer Science Koszalin University of Technology Koszalin, Poland kaczmarek.j@gmail.com, roberts@tu.koszalin.pl

Abstract—Control circuits for DC/DC converters are usually implemented as analog or digital transfer function (PID, type III etc.). These solutions are usually effective in the close vicinity of projected bias point, and its change causes worsening of stabilized output voltage properties. It's necessary to consider not only work mode (CCM, DCM), but also changes of bias point of the device. Main factors that influence bias point are: changes in loads resistance and changes in input voltage value. The solution to those problems could be using concept of controlling DC/DC converters using law of conservation of energy (project Bumblebee). During the work on the project Bumblebee characteristic oscillations in the steady state were observed. Similar oscillations occur in the current method (Current Mode) if do not use slope compensation coil current. The article shows the reason for this undesirable phenomenon and how to eliminate it.

*Keywords*—Law of conservation of energy, DC/DC converters, project Bumblebee

#### I. INTRODUCTION

Still a big problem for power supplies using DC-DC converters is to provide large power and stable output voltage for great changes in the output load.

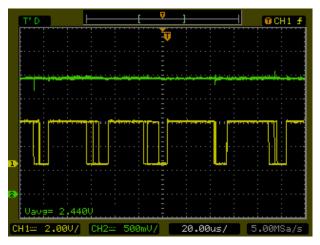

Fig. 1. PWM signal waveforms of tested prototype.

To meet this requirement, modern converters use advanced control methods for both Voltage Control Mode (VCM) and Current Control Mode (CCM) [1–10].

Another way of very good characteristic of output voltage stabilization (even with large load changes at the output) is the control method using the low of conservation of energy [11, 12]. The stability analysis of the converter based on this method is presented in [3]. Digital implementation of this method is presented in [13–16]. Based on the paper [13–15] the proposed solution obtains patent protection in the EU and USA [17, 18]. During further work on the prototype device presented in the paper [16] the inverter output voltage and coil current oscillations were observed in the case the value of duty cycle of the control PWM signal of the converter is greater than 0.5. The authors discussed the reason for this phenomenon and proposed a method to eliminate it. The oscillations of the PWM control signal of the prototype are shown in the Fig. 1.

## II. ALGORITHM USING LAW OF CONSERVATION OF ENERGY - PROJECT BUMBLEBEE

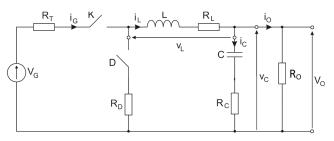

Equivalent circuit of power stage of Buck converter is presented in Fig. 2.

Fig. 2. Equivalent circuits the power stage of Buck converter.

An equivalent of the reference voltage (from Voltage Control Mode) is the reference energy  $E_{ref}$  (1), which can be defined as the sum of the energy stored in the power stage and transferred to out output load  $R_0$  in a single switching cycle in desired steady state. At the beginning of each cycle, the reference energy  $E_{ref}$ , is compared to the energy  $E_{P0}$  (2) stored in the power stage components. In this way, the energy that is drawn from the source  $V_G$  in the single switching cycle is determined. Based on the determined energy value  $E_X$  (3) and the actual operating point the control system calculates the duration of the duty cycle. For the sake of simplicity of the mathematical description, issues related to the parasitic elements of the power stage have been omitted.

Later in the paper, the equations applicable for a single switching cycle are shown.

$$E_{ref}(n) = \frac{1}{2} \cdot C \cdot V_{ref}^2 + \frac{1}{2} \cdot L \cdot \left(\frac{V_{ref}}{R_o(n)}\right)^2 + \frac{V_{ref}^2}{R_o(n)} \cdot T$$

(1)

where

$E_{ref}(n)$  – reference energy,

n - the number of converter switching cycle,

V<sub>ref</sub> - selected output voltage of converter,

C – capacitance of the capacitor,

L – inductance of the coil,

$R_O$  – load resistance of the converter in *n* switching cycle, number of converter switching cycle,

T – the duration of the switching cycle, where time range  $\langle nT, (n+1)T \rangle$

The energy stored in the converter and used by load converter in steady state at the beginning of cycle n can be described as:

$$E_{P0}(n) = \frac{1}{2} \cdot C \cdot V_C^2(n \cdot T) + \frac{1}{2} \cdot L \cdot I_L^2(n \cdot T) + \frac{V_{ref}^2}{R_0(n)} \cdot T \quad (2)$$

where

$E_{P0}(n)$  – energy stored in the power stage and used by load converter in steady state,

V<sub>C</sub>(nT) – average output voltage of converter,

I<sub>L</sub>(nT) – average current coil,

In order for the power stage output voltage Vo to have a set value Vref, it should be provided in each switching cycle:

- energy consumed at output load  $R_{0},$  in steady state when  $V_{0} = V_{\text{ref}},$

- recharge the energy stored in the power stage of converter.

Taking into account equations (1) and (2), in a single duty cycle we should deliver to the converter amount of energy defined by equation (3)

$$E_X(n) = \frac{C}{2} \cdot \left[ V_{ref}^2 - V_C^2(n \cdot T) \right] + \frac{L}{2} \cdot \left[ \frac{V_{ref}^2}{R_o^2(n)} - I_L^2(n \cdot T) \right] + \frac{V_{ref}^2}{R_o(n)} \cdot T$$

(3)

where

$E_X(n)$  – the energy that should be taken from the  $V_G$  source in the cycle n,

Taking into account that only in the duty cycle the converter gets energy from the  $V_G$ , and the whole current flows through the converter coil (Fig. 1), the amount of energy consumed by the converter during the duty cycle describes the following equation:

$$E_Z(n) = \int_{n \cdot T}^{n \cdot T + t_{on}(n)} V_G(t) \cdot I_L(T) dt$$

(4)

where

- $E_Z(nT)$  the energy that have be taken from the source in the cycle *n*,

- $t_{on}(n)$  duration of duty cycle in switching cycle n,

- $V_G(t)$  supply voltage for the converter during the actual cycle,

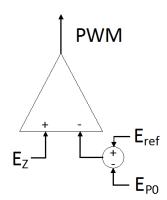

The simplified block diagram of the analog control unit of the converter power stage is shown in Fig. 3.

Fig. 3. The simplified block diagram of the analog control unit.

## III. SUB-HARMONIC OSCILLATIONS

The control unit of the converter determines the duty cycle time in which the energy is drawn from the  $V_G$  source of the converter power stage. This ensures that in steady state the average amount of energy accumulated in the coil and capacitor is constant. The current flowing through the coil increases in the duty cycle and decreases for the rest of the cycle.

The task of the control unit is to select duty cycle duration so that the average value of the coil current (and its energy) is at the fixed level.

If the converter's control signal duty cycle is greater than half the converter's switching period ( $t_{on} > = 0.5T$ ), then the average coil current in two successive duty cycles may be unchanged, but the PWM values for these two periods will be completely different. This phenomenon also occurs in the current control (PCM) of the power stage and is well known [19–24].

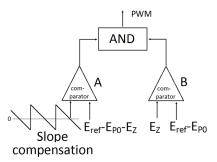

To eliminate this unfavorable phenomenon, additional technique of slope compensation of the coil current value is introduced in the current control mode. In current control mode (PCM), the circuit that compensates for the coil current slope is generally autonomous. An important issue in current control is to adjust the slope of compensating signal to the coil current value in a steady state (the value of the average coil current depends on the output load resistance). The same solution can be applied to the presented method based on the law of conservation of energy. In that case, there is a simpler solution. The second comparator can be applied to compare slope compensation signal of the coil current with the amount of energy that still needs to be delivered to the converter power stage in the  $E_{ref}$ - $E_{P0}$ - $E_Z$  duty cycle. In this way, the value of the DC component of the slope compensation signal from the average value of the coil current becomes irrelevant. A schematic diagram of a PWM modulator with slope compensation of the coil current is shown in Fig. 4.

Fig. 4. Slope compensation ramp.

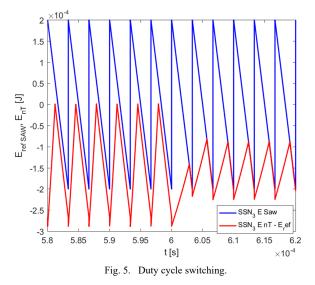

Comparator B controls the amount of energy to be delivered to the converter power stage (performs comparator functions from Fig. 3). Comparator A includes the slope compensation of the coil current. If the duty cycle of the switching signal is greater than 50 % ( $d_a \ge 0.5$ ) then comparator A will change its state earlier than comparator B. Principle of operation of the slope compensation of the coil current is shown in Fig. 5.

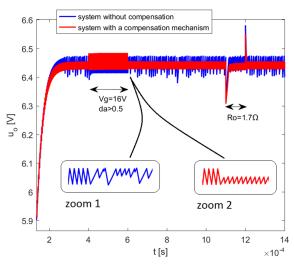

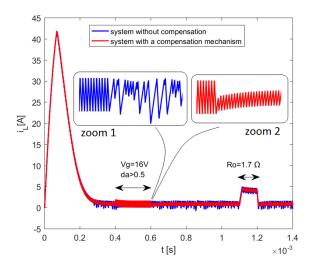

Fig. 5 shows the signals at the input of comparator A, blue line indicates the slope compensation signal for the coil current. As long as the inequality is satisfied that the duty cycle of the switching signal is lower than 50% (da<0.5), comparator A will not work. At time  $t = 6 \cdot 10^{-4}$ s, the value of the PWM ON/OFF factor d<sub>a</sub> is increased to above 0.5 and the comparator A changes its state earlier than comparator B. Changing the coefficient d<sub>a</sub> is due to a step change in the supply voltage. The correctness of the proposed solution is confirmed by the results of the simulations. Figures 6 and 7 show variations in the output voltage V<sub>0</sub> and I<sub>L</sub> coil current of the converter power stage for control circuits without coil slope compensation function and with this function.

#### IV. SIMULATION-BASED RESEARCH STUDIES

Simulation of the proposed circuit was performed in MATLAB/SIMULINK and Simscape, without the use of equivalent small signal models of the converter power stage. In

simulation power stage of Buck converter was the same as / (identical to) power stage in Texas Instruments TMDSC2KWRKSHPKIT Development Board

According to the documentation of the Development Board, it was assumed that equivalent circuit parameters are:

$$L = 10 \ \mu H, R_L = 42.4 \ m\Omega, C = 726 \ mF, R_C = 40 \ m\Omega, R_O = 7\Omega$$

$R_{K1ON}$  = 5 m $\Omega,~R_{K2ON}$  = 1.1 m $\Omega$  (drain to source resistance in ON state)

$f_s = 300 \text{kHz}, V_G = 9 \text{ V}, V_{ref} = 6.45 \text{ V}$

The voltage change from  $V_G = 9V$  to  $V_G = 16$  V occurs at the time  $t = 4 \cdot 10^{-4}$ s, and voltage change from  $V_G = 16$  V to  $V_G = 9V$  occurs at the time t=  $6 \cdot 10^{-4}$  s

The output load change from  $R_0 = 7 \Omega$  to  $R_0 = 1.7 \Omega$  occurs at the time  $t = 11 \cdot 10^{-4}$ s, and voltage change from  $R_0 = 1.7 \Omega$  to  $R_0 = 7 \Omega$  occurs at the time  $t = 12 \cdot 10^{-4}$  s.

Fig. 6. Voltage Vo changes that occur due to VG and Ro changes.

Fig. 7. Current coil changes that occur due to  $V_G$  and  $R_O$  changes.

Fig. 6 shows voltage  $V_0$  changes that occur due to  $V_G$  and  $R_0$  changes. Red line - circuit with slope compensation of the coil current. Blue line - voltage  $V_0$  waveform without slope compensation of the coil energy changes. Zoom 1 and Zoom 2 show the output voltage waveforms zoomed in.

Fig. 7 shows coil current  $I_L$  changes that occur due to  $V_G$  and  $R_O$  changes. Red line - circuit with slope compensation of the coil current. Blue line - current  $I_L$  waveform without slope compensation of the coil energy changes. Zoom 1 and Zoom 2 show the output coil current waveforms zoomed in

#### V. CONCLUDING REMARKS

Using the law of conserving energy to stabilize the output voltage of the converters provides very good dynamic parameters of the stabilized voltage because in each switching cycle changes in supply voltage and converter output load are taken into account. An important limitation of the method is the output voltage sub-harmonic oscillations similar to those observed for current control (PCM – Peak Current Mode), shown in Fig. 6 and 7. Authors presented the causes of origin of this unfavorable phenomenon and proposed an effective and simple way to eliminate it (Fig. 4). Further work on the development of the method, especially for digital control systems, is planned.

#### REFERENCES

- M. Athans, "A Tutorial on the LQG/LTR Method", 1986 American Control Conference, 1986, vol. 582, no. 606, pp. 1289–1296.

- [2] A. Babazadeh, D. Maksimovic, "Hybrid Digital Adaptive Control for Fast Transient Response in Synchronous Buck DC-DC Converters", IEEE Trans. Power Electron., vol. 24, no. 11, pp. 2625–2638, 2009.

- [3] A. Babazadeh, D. Maksimovic, "Hybrid digital adaptive control for synchronous buck DC-DC converters", 2008 IEEE Power Electronics Specialists Conference, 2008, vol. 24, no. 11, pp. 1263–1269.

- [4] P. Cortes, M. P. Kazmierkowski, R. M. Kennel, D. E. Quevedo, J. Rodriguez, "Predictive Control in Power Electronics and Drives", IEEE Trans. Ind. Electron., vol. 55, no. 12, pp. 4312–4324, 2008.

- [5] G. Eirea, S. R. Sanders, "Adaptive Output Current FeedforwardControl in VR Applications", IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1880–1887, 2008.

- [6] S. Mariethoz, S. Almer, M. Baja, A. G. Beccuti, D. Patino, A. Wernrud, J. Buisson, H. Cormerais, T. Geyer, H. Fujioka, U. T. Jonsson, C.-Y. K. C.-Y. Kao, M. Morari, G. Papafotiou, A. Rantzer, P. Riedinger, "Comparison of Hybrid Control Techniques for Buck and Boost DC-DC Converters", IEEE Trans. Control Syst. Technol., vol. 18, no. 5, pp. 1126–1145, 2010.

- [7] J. Neely, S. Pekarek, R. DeCarlo, "Hybrid Optimal-Based Control of a Boost Converter", 2009 Twenty-Fourth Annu. IEEE Appl. Power Electron. Conf. Expo., pp. 1129–1137, 2009.

- [8] H. Peng, D. Maksimović, "Digital current-mode controller for DC-DC converters", Appl. Power Electron., 2005.

- [9] N. Phurahong, S. Kaitwanidvilai, "Fixed structure robust 2DOF Hinfinity loop shaping control for ACMC buck converter using genetic algorithm", 2012 9th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, 2012, vol. 2, no. 1, pp. 1–4.

- [10] M. Veerachary, G. Satish, "First-order pseudo dead-beat current controller for buck converter", INTELEC 2009 - 31st Int. Telecommun. Energy Conf., pp. 1–6, 2009.

- [11] J. Kaczmarek, A. Mazurek, "New Concept of DC/DC Converters Digital Control Based on Law of Conservation of Energy - Project Bumblebee", 2007 14th International Conference on Mixed Design of Integrated Circuits and Systems, 2007, pp. 586–591.

- [12] P. Gupta, A. Patra, "Energy Based Switching Control Scheme for DC-DC Buck-Boost Converter Circuits", Analysis, no. 1, pp. 1525–1529, 2005.

- [13] P. Gupta, A. Patra, "Super-Stable Energy Based Switching Control Scheme for DC-DC Buck Converter Circuits", 2005 IEEE Int. Symp. Circuits Syst., pp. 3063–3066, 2005.

- [14] J. Kaczmarek, A. Mazurek, "Comparison of classic DC/DC converters with converters equipped with analog-digital regulator based on law of conservation of energy (bumblebee type)", Proceedings of the 14th International Conference "Mixed Design of Integrated Circuits and Systems", MIXDES 2007, 2007, pp. 564–569.

- [15] J. Kaczmarek, A. Mazurek, "Compensation of Calculations Duration on Converters Output Voltage in Digitally Controled Converters Based on Law of Conservation of Energy - Project Bumblebee", 2007 14th Int. Conf. Mix. Des. Integr. Circuits Syst., pp. 412–417, 2007.

- [16] J. Kaczmarek, A. Mazurek, "Measurement results of buck converter prototype digitally controlled by algorithm using law of conservation of energy - project Bumblebee", Mixed Design of Integrated Circuits and Systems, 2008. MIXDES 2008. 15th International Conference on, 2008, pp. 525–530.

- [17] H. S. 5QL (GB) Schiff, Albrecht Johannes Southampton, "Switch mode power converter with energy based switching control EP 2 894 779 A1", EP 2 894 779 A1, 2015.

- [18] W. (GB) Albrecht Johannes SCHIFF, "Patent No: US 20150200591/A1", US 2015/0200591 A1, 2015.

- [19] R. Sheehan, "UNDERSTANDING AND APPLYING CURRENT-MODE CONTROL THEORY", Power Electronics Technology Exhibition and Conference. Citeseer, 2007.

- [20] Young-Seok Jung, Jun-Young Lee, Myung-Joong Youn, "A new small signal modeling of average current mode control", PESC 98 Record. 29th Annual IEEE Power Electronics Specialists Conference (Cat. No.98CH36196), 2002, vol. 2, pp. 1118–1124.

- [21] R. Ridley, "A More Accurate Current-Mode Control Model", Unitrode Seminar Handbook, SEM—100, pp. 1–11.

- [22] D. J. Perreault, G. C. Verghese, "Time-varying effects and averagig issues in models for current-mode control", IEEE Trans. Power Electron., vol. 12, no. 3, pp. 453–461, 1997.

- [23] S. Chattopadhyay, S. Das, "A Digital Current-Mode Control Technique for DC–DC Converters", IEEE Trans. Power Electron., vol. 21, no. 6, pp. 1718–1726, 2006.

- [24] R. Poley, A. Shirsavar, "Digital Peak Current Mode Control with Slope Compensation using the TMS320F2803x", Texas Instruments, no. June. pp. 1–28, 2010.